La memoria virtual

(18 páginas)

1. Dos problemas relacionados con la gestión de la memoria

- Protección de los procesos: En general, los procesos no deben tener acceso libre a la memoria física

- Espacio de memoria disponible: Es deseable contar con más espacio disponible que el que da la memoria principal

Memory Management Unit (MMU) gestiona las dos soluciones a tales problemas

2. Solución 1: Espacio de direccionamiento virtual

Para la protección de los procesos se utilizan direcciones virtuales (Hay que traducirlas a direcciones físicas).

2.1. Direcciones virtuales y físicas

2.1.1. Prespectiva del proceso (dirección virtual)

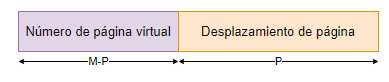

- Memoria virtual: Es de M palabras

- Paginas: Son de P palabras (ej. 8 bits) y se dedicarían a decir a qué palabra quiero acceder en cada momento dentro de la pagina.

- Página virtual: El resto de bits (M-P bits) indicaría a qué pagina virtual quiero acceder dentro de ese proceso.

2.1.2. Prespectiva del hardware (dirección física)

- Memoria física: Es de N palabras

- Marcos: Son de P palabras

- Nº de marco: Lo indica los N-P primeros bits

(Inserte distribución de bist página 8)

2.2. Traducción de direcciones

(Inserte gráfico página 9)

2.3. El direccionamiento virtual y la eficiencia

Obviando los fallos de página, ¿cuántos accesos a memoria (física) requiere un acceso a una dirección virtual?

2 accesos: Primero: Se debe acceder a la tabla de página, que está en memoria física, para obtener así la traducción de la dirección virtual. Segundo: Acceder a la dirección efectiva, una vez se obtiene la dirección real física tras la traducción, se dirige a dicha dirección para leer la palabra.

Aunque esto supone un empeoramiento de la eficiencia es necesario por la protección de los procesos y el espacio de almacenamiento. Para solucionar este problema surge uan especie de caché para las traducciones de página. Esto es lo que se conoce como TLB

3.4. Mejora de eficiencia: TLB

Buffer de Traducción Lateral (Translation-lookaside Buffer – TLB)

- Caché de traducciones de direcciones virtuales a físicas

- Estructura HW en la MMU

- Se pregunta primero a la TLB, y si no, se acude a la tabla de páginas

- Gran variedad de diseños (Tamaños y Asociatividad)

- Reemplazo muchas veces aleatorio

3. Solución 2: Memoria virtual

Para aumentar el espacio de memoria disponible para los programas

3.1. Memoria virtual paginada

Análogo a la caché (Bloque ≈ Página, Fallo de caché ≈ Fallo de página).

El tamaño de página y tamaño de marco es lo mismo. Pero no necesariamente hay más páginas que marcos.

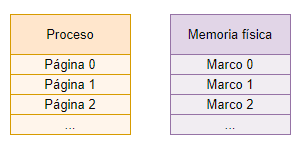

3.2. Tabla de páginas

Para traducir una dirección virtual a una física se utiliza lo que se conoce como tabla de página. Hay una Tabla de página por proceso, es dedicada a cada proceso.

(inserte gráfico donde se ve la traducción usando tablas de páginas)

- Bits de control

- Puntero (Marco en memoria física y posición(bloque) en almacenamiento secundario)

- Almacenada en memoria: Solo tablas muy pequeñas se almacenan en registros

- Apuntada por un registro: Page-Table Base Register (PTBR)

- Múltiples estructuras posibles: Veremos solo la más simple

La dirección a la que apunta el PTBR, ¿es virtual o física?

Física, porque si no no tendría con qué traducirla. Es el mecanismo para traducir las direcciones virtuales a físicas.

Si se tiene un acierto, entonces se hace la traducción para accesar la memoria principal

Si se tiene un fallo de página entonces va al almacenamiento secundario.

3.3. Fallos de página: Decisiones de diseño

(inserte gráfico de la proporcionalidad Tamaño grande Tamaño pequeño)

- Asociatividad

- Mecanismo de escritura

3.4. Combinación memoria virtual y caché

(Inserte gráfico página 17)