Tipos de memoria

(16 páginas)

1. Memorias estáticas: SRAM

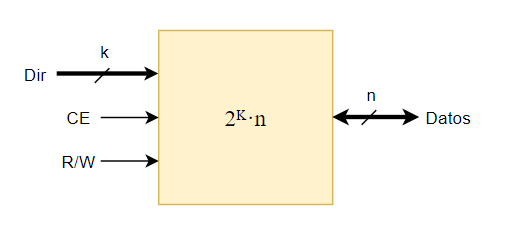

1.1. SRAM asíncrona

Tecnología que emplean las cachés, y solamente requieren una fuente de alimentación para mantener su estado. Pueden ser síncronas o asíncronas. Son más rápidas que las DRAM pero tienen menos capacidad de almacenamiento.

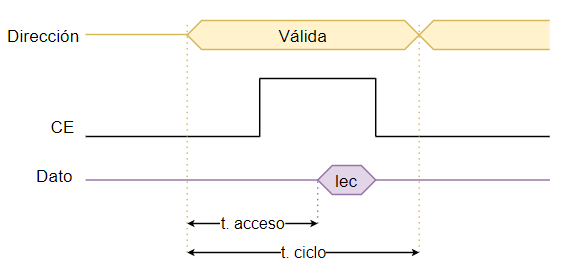

1.1.1. Ciclo de lectura

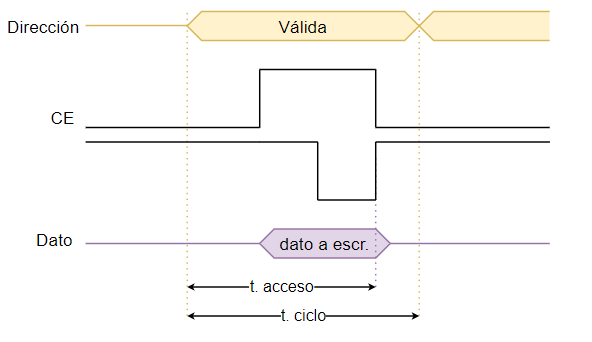

1.1.2. Ciclo de escritura

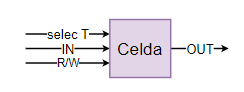

1.1.3. Celda básica

La unidad básica de almacenamiento es lo que llamamos celdas. Es el módulo más básico, y en el caso de las SRAM equivale a biestables.

Una celda es 4x4 (4 palabras de 4 bits cada una)

¿Por qué se usan estructuras matriciales?

Por la longitud de las líneas

¿Tiene alguna desventaja utiliza estructiras más lineales?

1.1.4. Esquema general

2. Mapa de memoria

Conjunto de todas las posibles direcciones a las que puede acceder un procesador mediante sus buses de datos, direcciones y control.

Por ejemplo, 16 líneas de direcciones y 8 de datos nos lleva a un mapa de 64K posiciones de 8 bits cada una.

2.1. Mapa de memoria y E/S

2.1.1. E/S mapeada en memoria

- Si la memoria física ocupa menos que la capacidad de direccionamiento

- Se usa parte del espacio de direccionamiento para dispositivos de E/S

2.1.2. E/S independiente

- Existe un espacio de direcciones diferente

- Se decide el uso del bus de direcciones mediante una señal de control ( 𝐼𝑂/𝑀 )

3. Memorias dinámicas: DRAM

Ademas de una fuente de alimentación necesitan ser refrescadas periodicamente. Ahora en vez de ser transistores, se basan en un condensador y un circutio de conmutación transistorizado. En menos espacio se puede tener mucha más capacidad.

Ejemplo estructura interna 64K x 1

3.1. Mejoras

3.1.1. El entrelazado

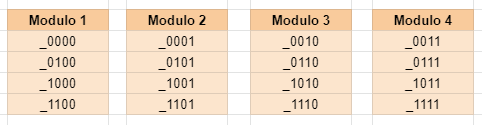

Supón que dispones de 4 módulos de DRAM de 4 palabras cada uno. Quieres construir una memoria de 16 palabras. Fácil, ¿no? En lugar de hacer que los bit significativos de la palabra definan el módulo (XX)XX, haremos que los mneos significativos sean los que definen el modulo XX(XX). Esto se hace así, porque a nivel de eficiencia se puede evadir el tiempo de refresco para acceder a otra palabra del modulo al que ya se ha accdido proeviamente.

3.1.2. Otras

3.1.2.1. CDRAM (Cache DRAM)

- Incluye pequeña memoria SRAM que actúa como caché de las últimas filas accedidas.

- Accesos más rápidos para datos de filas recientemente accedidas

- Simultanear una lectura o escritura con el refresco de la memoria.

3.1.2.2. SDRAM (Synchronus DRAM)

- Utiliza una señal de reloj externa para sincronizar su intercambio de datos con el procesador

- Incluye una pequeña memoria SRAM que recoge la dirección y la orden

- Responde después de un número determinado de ciclos de reloj. E

Ejemplo: DDR, capaces de escribir/leer más de una palabra por ciclo (2 la DDR, 4 la DDR2, 8 la DDR3…)

3.1.2.3. RDRAM (Rambus DRAM)

- Sustituyen las líneas de selección de fila y columna por un bus entre la DRAM y el procesador.

- Superada en una guerra de patentes por la SDRAM, más barata y, al final, también con mejor rendimiento.

Ejemplo: Memoria de la Nintendo 64 o la PS2.