El bus como estructura de interconexión

(42 páginas)

1. Introducción

Un bus es el elemento de interconexion entre sistemas del ordenador. Pero existen muchos buses de características muy diferentes. “Camino” que permite comunicar de forma selectiva un determinado número de componentes/dispositivos de acuerdo a un conjunto predefinido de reglas de conexión.

El principal bus es el bus del sistema que comunica CPU, memoria, y dispositivos E/S. Se divide en un bus de datos, bus de direcciones y bus de control (funcionalmente).

- Datos: Comunica datos de un lado a otro (Su ancho se relaciona con el tamaño de palabra que se usa en el sistema)

- Direcciones: Está relacionado con la memoria (Su ancho se relaciona con el número de direcciones diferents a las que puedo acceder. Toene que ver con el MAR)

- Control: Interrupciones, E/S, lectura escritura. Señales a intercambiar según el tipo de protocolo.

2. Características de los buses

2.1. Grado de paralelismo

- Serie: bit a bit

Menoss bit en la unidad de tiempo,

- Paralelo: Caracterizados por un ancho. Transmitimos un ancho de bits.

Más bit en la unidad de tiempo

Diferencia del tiempo de llegada de cada línea. Los bit empiezan a sesgarse y llegan en diferentes momentos en incrementos de velocidad. Se limita la velocidad del bus.

Diafonía (crosstalk): Interferencias, la señal de un clable se ve afectada por otro debido a inducción electromagnéetica. A más líneas en paralelo mas crosstalk.

- Multiplexado: Las mismas líneas se usan para fines diferentes en el mismo isntante de tiempo.

¿Es más rapido un bus en serie o en paralelo?

Con las mismas condiciones/frecuencia de transmisión es más rapido uno en paralelo. Pero en el otro caso, el bus paralelo no simepre será más rpaido que el serie debido a dos limitaciones (Limitaciones del paraleismo en los buses)

2.2. Direccionalidad

- Unidireccional: En un único sentido

- Half-Duplex (semidireccional): En ambos sentidos pero no a la vez

- Full-Duplex: En ambos sentidos permitiendo que sea al mismo tiempo.

2.3. Ancho y velocidad (Rendimiento)

La velocidad que consigo con un bus.

- Ancho: Numero de bits que pueden transmitirse simultaneamente

- Frecuencia: Cada cuanto tiempo se envía dicho ancho.

- Latencia: Tiempo nececario para enviar 1 dato concreto.

- Velocidad sostenida (Ancho de banda): El flujo de datos que puedo enviar en la unidad de tiempo.

Tienes un bus de ancho 16 bits, que puede transmitir a una frecuencia de 133 MHz, ¿cuál es su velocidad de transferencia (en Mbits seg y en MB/ seg

2.128 Mbps = 266 Mbytes/s

2.4. Modularidad

2.5. Fiabilidad

Si el computador tiene un solo bus, esto supone un punto de fallo critico, si ese único bus falla, falla todo, pero a más buses, el computador es más tolerante a fallos y se obtiene redundancia. Esto se puede extrapolar a sistemas grandes donde interesa la redundancia, ya que en PCs pequeños es dificil imaginarlo.

2.6 Capacidad de conexión

Número máximo de dispositivos que pueden conectarse

2.7. Métodos de sincornización

- Sincronos: Usan una señal de reloj

- Asíncronos: Comunicación por eventos

- Semisícrono: En cada ciclo de reloj debe poder establecerse la comunicación. Los dispositivos más rápidos esperan por los más lentos.

2.8. Protocolo de estrategia de control

- Centralizada: Un elemento…

- Distribuida: Una estructura que se encarga del control de todo

2.9. Extensión física

Cómo voy a transmitir los datos, con distintos buses, bus de micras, etc. Influye en la velocidad, el número de conexiones…

A medida que el bus empieza a ser grande, tengo que tener cuidado con las cosas que se transmiten porque el efecto de los cambios a la velocidad de la luz, si el bus tiene una cierta extensión haber confusión con los datos en la sincronización. Esto sucede con buses muy grandes.

3. Tipos

3.1. Según el número de elementos interconectados

- Punto a punto: Buses dedicados

- Modular

- Poco rendimiento

- Bus compartido: Bus donde conecto distintos elementos al mismo bus.

- No modular (poco escalable)

- Alto rendimiento

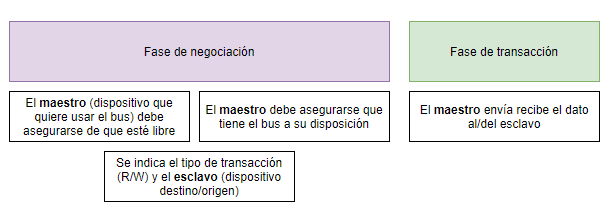

1) Adquisición: El intento de convertirse en master

2) Selección destino: Es la intención de comunicarse con otro elemento que va a intervenir en la comunicación.

3) Selección del tipo de transacción (lectura o escritura)

4) Envío o recepción del dato.

5) Sesión: Dejar el bus preparado para que otro más lo use (renunciar a ser master)

Supongan que tienen un sistema con 4 dispositivos que comparten un bus. Planteen un protocolo para negociar el acceso al bus. ¿Cómo sería? ¿Qué pasos tendría?

El elemento pide acceso al bus con una señal de request a un dispositivo adicional, si el bus está libre darle la opción de entrar al bus y si no, ponerlo en una especie de lista de espera.

- Redes de medio conmutado:

Ej: tengo N=3 elementos que quiero conectar mediante un bus.

Podría conectarlos con buses dedicados en anillo. Si N incrementa, se crea una malla y comienza a aumentar las

interconexiones. Por cada N que añada se crean cada vez más interconexiones, sin embargo, dota de alto

rendimiento al tener conexiones dedicadas/directas.

En un único bus no supone ningún coste añadir nuevos elementos, pero supone menos rendimiento a medida que incrementa N

porque los elementos se disputan el uso del mismo medio de transmisión. Es necesario implementar un arbitraje/protocolo

(Decidir quien puede estar en posesión del (dscribir en el) bus), turnar los elementos. Un ejemplo sería el arbitraje

master/slave (Sólo el maestro tiene potestad de escribir en el bus y el maestro se va rurnando), la velocidad será

menor porque la decisión para elegir el maestro consume tiempo.

4. Fase de negociación

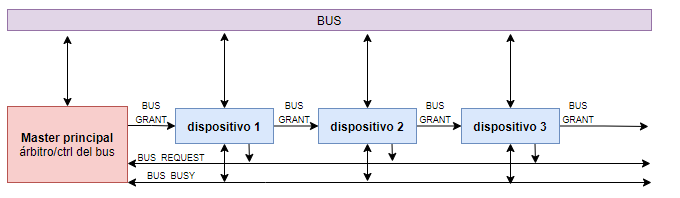

4.1 Ejemplo Daisy Chaining (Cadena de margarita)

No se controla quién tiene la línea ocupada.

1) Activa la línea BUS REQUEST

2) El árbitro activa el GRANT cuando detecta el REQUEST activado y BUSY desactivado

3) Cuando un dispositivo detecta un flanco de subida de GRANT

- Si no habia solicitud: pasa la señal del GRANT al otro dispositivo

- Si habia solicitado el bus: (REQUEST activo toma el control del bus cuando el bus quede libre (BUSY desactivado)

4) Toma el control (Se desactiva REQUEST y se activa BUSY)

5) En cuanto se activa BUSY se desactiva GRANT

6) Al finalizar la transacción se desactiva BUSY

1. ¿Es “justo” este protocolo?

No porque no se respeta el orden de qué dispositivo estaba antes pidiendo el uso del bus, ya que mientras la linea esté en BUSY no puede comprobar quién pidió primero el bus, y si en el momento de mirar quien están solicitando, hay dos o más dispositivos esperando siempre se lo va a dar primero al dispositivo que esté antes en la serie de la coneción física.

2. Tal como está el protocolo, ¿podemos realizar la “negociación” de quién será el siguiente dispositivo en usar el bus al mismo tiempo que se usa el bus?

Mientras se esta usando el bus no puede negociarse nada porque no se puede hacer la acción de otorgar el uso del bus hasta que no deje de usarse .

3. Tal como está planteado el protocolo de cadena de margarita, ¿qué ocurre si se estropea el primer dispositivo de la cadena

Si se rompe uno de los dispositivos, como están conectados en serie ya los demás dispositivos que le sucedan nunca podrán solicitar un REQUEST

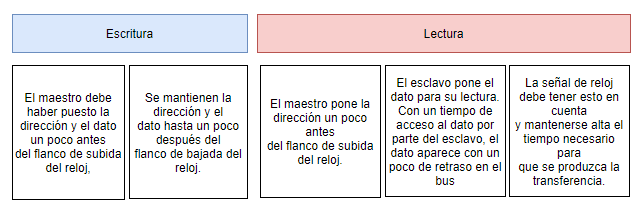

5. Fases de la transacción típica en un bus compartido

- Sincrónica: Reloj común o individual para cada dispositivo (Se hace una vez se tiene el bus, pues Daisi Chaining es asínrono) El reloj corta el uso del bus poco después de que un ciclo de reloj dé lugar tras suponer que la acción lectura o escritura dio lugar en el tiempo que se le fue concedido.

- Asincronica: Se intercambia información que indica cuando comienza y finaliza la transacción Se utilizan dos lineas MASTER y SLAVE

¿Cuál modo de comunicación es mejor?

El asíncrono es más flexible. El sincrono es más rápido porque tiene menos overhead.

6. Jerarquía de buses

- Buses internos de los circuitos integrados: Buses chiquitos muy rápidos, en general son síncronos y sus protocolos suelen ser secreto.

- Buses de circuito impreso: Son un poco más lentos y pueden tener varios centímetros de longitud. Suelen ser síncrnos. Ejemplo: wishbone (Estandar abierto), Quick Path Interconect (Intel), Hiper Transport (AMD, Cisco)

- Buses del plano posterior o Backplane: Circuitos de placa para conectar circuitos integrados entre sí (PCI, PCIExpress, Future Bus)

- Buses de E/S: Puden ser más rapidos mas lentos sincronos o asíncronos. (USB, SATA, Firewire)

- Redes de computadores: (TCP/IP, token Ring, Ethernet)

6.1. Jerarquía típica

(Insertar esquema de jerarquía de buses página 38)

7. Clasificación de estructuras de buses

7.1. Búses múltiples

Cada dispositivo tiene interfaces a los buses.

- Alta redundancia y fiabilidad

- Alta velocidad

(ilustración Página 33)

7.2. Crossbar

- Se utliza para conectar dos grupos de unidades diferntes

- Solo se puede tener activado un punto d econmutación por fila y por columna

- El número máximo de comunicaciones simultáneas es de k=min(fila,columna)

(ilustración Página 34)

7.3. Conmutador/Switch

- Permite una comunicación limitada aunque simultánea, entre cualquiera de los elementos a los que está conectado. Está limitado a un ancho de banda concreto.

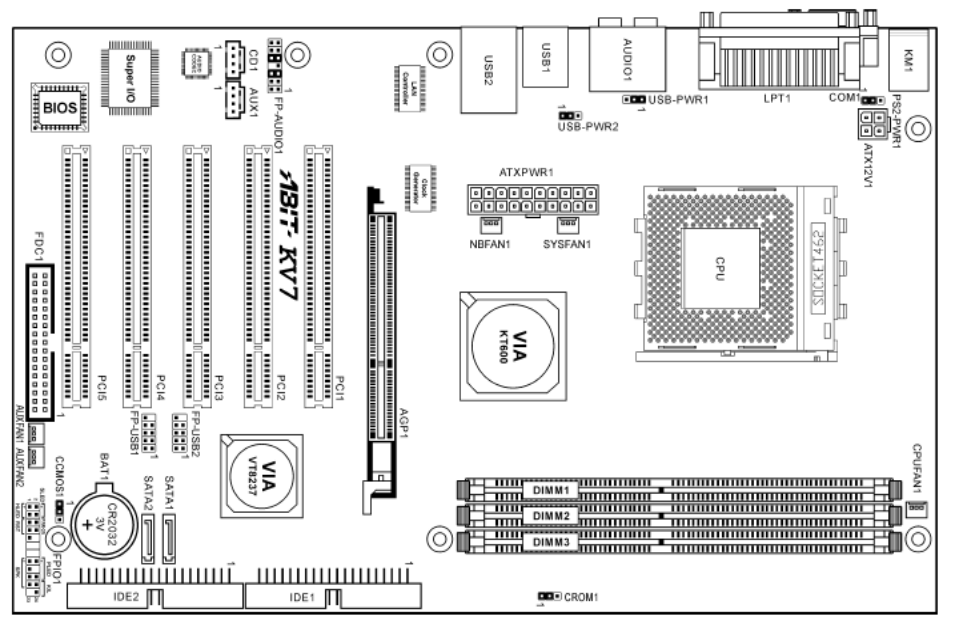

8. Ejemplos de buses reales

8.1. PCI (Peripheral Component Interconnect)

- Estándar de facto para la conexión de tarjetas de video, sonido y red en los PC de los 90 y primeros años del 2000.

- Bus de plano posterior (Aunque también puede utilizarse como bus de E/S.)

- Su popularidad se debió a que permitía la conexión con otros buses y se implementaba con pocos circuitos integrados, lo que lo convertía en una alternativa económica.

8.1.1. Más información

- Bus paralelo (32 bits), síncrono (reloj de 33.33MHz) y half-duplex

- Velocidad de transferencia pico de 133 MB/seg

- Velocidad de transferencia pico de 133 MB/seg

- Puede configurarse para trabajar con 32 o de 64 bits.

- Comparte 32 líneas para datos y direcciones mediante una multiplexación en el tiempo

8.1.2. Funcionamiento

- Sistema de arbitraje centralizado y asíncrono

Cada maestro tiene una única señal de petición REQ y una señal de concesión GNT.

El protocolo no establece cómo debe implementarse este arbitraje.

- Transacción del bus PCI

fase de direcciones (address phase)

seguida de una o más fases de datos (data phases)

8.3 PCI express

- Bus Serie Full-dúplex

- No es exactamente un bus, sino una red de conmutación

- Usa hasta 32 “carriles” (lanes: x1, x2, x4, x8, x16, x32)

Cada carril contiene dos pares de líneas, un par para enviar datos y otro para recibirlos

Data striping cuando utiliza más de un carril