La memoria Caché

(30 páginas)

1. Principios de la caché

- Estructura puramente hardware. Transparente para el software.

- Entre memoria principal y CPU. Aunque el término denomina también otras estructuras entre dos niveles cualquiera de la jerarquía de memoria.

- Busca mejorar la velocidad de acceso.

- Menos capacidad que el nivel superior. Pero debe ser capaz de almacenar cualquier dirección de memoria.

1.1. Localidad de referencia

- Localidad espacial: Se suele acceder de forma consecutiva a direcciones próximas de memoria. Cuando se accede a una posición de memoria, se trata de cargar el bloque de direcciones adyacente.

- Localidad temporal: Se suele acceder a las mismas direcciones de forma repetitiva en el tiempo. Una vez que se trae un bloque de memoria, se trata de mantenerlo (evitar un reemplazo) en la caché el máximo tiempo posible

La memoria almacena instrucciones y datos ¿Se comportan de forma similar o diferente con respecto a las diferentes dimensiones de la localidad de referencia?

Como los procesadores tienen cachés diferenciadas para instrucciones y para datos, se supone diferentes formas de funcionamiento en diferentes cachés.

1.2. Funcionamiento de la caché

1.2.1. Lecturas

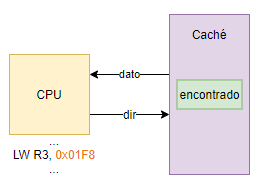

- Acierto (hit) tras lectura

Para acceder a la caché se necesita además de indicar el valor, hay que indicar de donde proviene ese valor. La CPU manda la dirección al bus de direcciones, y la caché lee lo que le llega por el bus de direcciones.

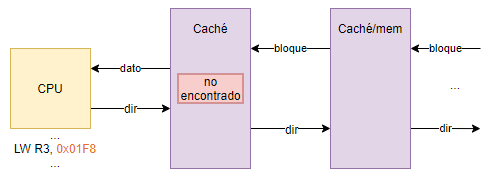

- Fallo (miss) tras lectura

No se carga todo el bloque en la caché antes de leer el dato. Es decir si un bloque tuviera 18 palabras de memoria, no debería cargarse todo el bloque, porque tiene un costo.

Ante un fallo ¡hay que parar el procesador! Es posible la “lectura de comienzo inmediato” (load-through)

1.2.2. Métricas

- Frecuencia de aciertos: Porcentaje de aciertos sobre el total de accesos

- Frecuencia de fallos: Porcentaje de fallos sobre el total de accesos

- Tiempo de acierto: Tiempo necesario para obtener un dato que se encuentra en caché. Tiempo de acceso + tiempo para saber si se encuentra allí

- Penalización por fallo: Tiempo para traer el dato desde el nivel inferior

- Tiempo de fallo: Tiempo de acierto + penalización por fallo

1.2.3. Escrituras

- Escritura directa (write-through)

- Escritura retardada (write-back)

1.2.4. Coherencia en sistemas multicore

2. Mapeado

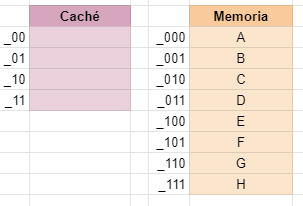

Supongamos que disponemos de un sistema de bloques de una palabra (por simplificar). Nuestra caché tiene 4 líneas y la memoria es de 8 palabras; por lo tanto, necesitaremos 3 bits para direccionar esa memoria.

Tenemos un programa que accede a las siguientes direcciones: 000, 001, 011, 001, 101, 010

1. ¿Cómo ubicamos esos bloques en la caché?

2. Ante cada nuevo acceso, ¿cómo se sabe si la caché ya contiene ese bloque?

3. ¿Qué hacemos cuando la caché se llene?

Las técnicas de mapeado permmiten decidir en qué línea de la caché almacenar un bloque de la memoria. dentificar con qué bloque de la memoria principal se corresponde el contenido de una línea de la caché usando eqtiquetas.

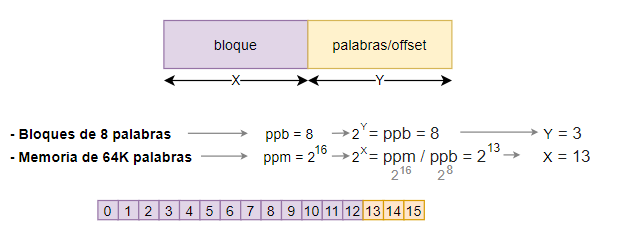

Supongamos una memoria compuesta de dos conjuntos de información

- Bloque: Infdica en que bloque de la memoria está esa direccion

- Palabra (offset): Que palabra dentro de ese bloque es la que estoy intentando acceder

1.1. Dirección de memoria desde la perspectiva de la memoria principal

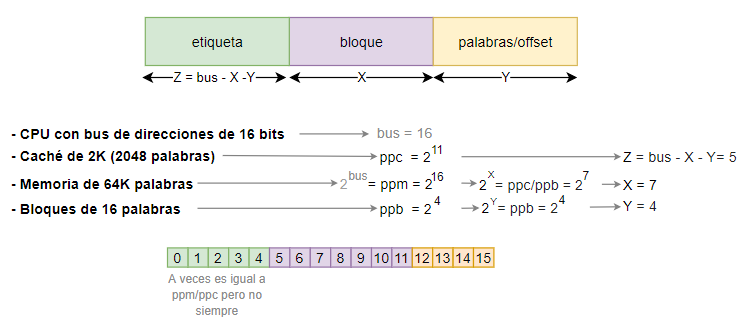

1.2. Mapeado directo

Se introduce el concepto de etiqueta, que hace referencia a la dirección de la caché que puede estar asociada a múltiples direcciones de la memoria pricnipal (bloque+offset)

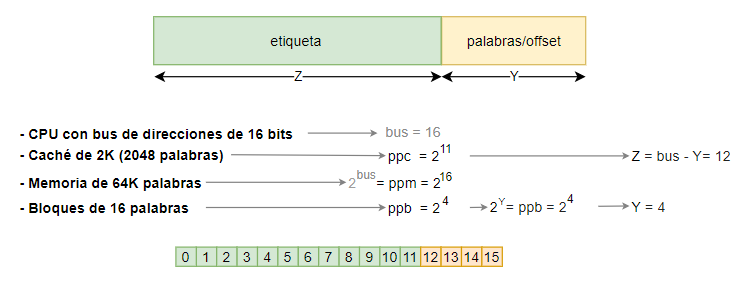

1.3. Mapeado completamente asociativo

- Coloca cada nuevo bloque en la primera posición libre de la caché. (Etiquetas mayores y hace posible comprobar todas las etiquetas simultáneamente)

- Memoria asociativa: hardware más complejo y caro (incremento exponencial del coste en relación al número de bloques)

- La información del bloque pasa a ser absorbido por la etiqueta.

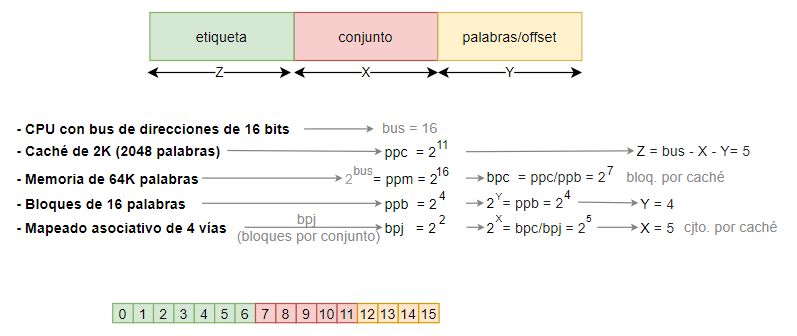

1.4. Mapeado asociativo por conjunto

- A medio camino entre los otros dos métodos

- Agrupa las líneas de la caché en conjuntos (vías: lineas por conjunto (lpc))

- El conjunto se usa como en el mapeado directo

- Dentro de cada conjunto se puede ubicar el bloque en cualquier línea de forma asociativa

1.5. Reemplazamiento

Cuando la caché se llena, existes diferentes algoritmos para reemplazar las direcciones guardadas. Para el mapeado directo no es necesario utilizar una estrategia de reemplazo.

- Reemplazamiento First in, first out (FIFO)

- Reemplazamiento First in, first out (LRU)

1.5.2. Escritura

- Escritura directa (write-through)

- Escritura retardada (write-back)

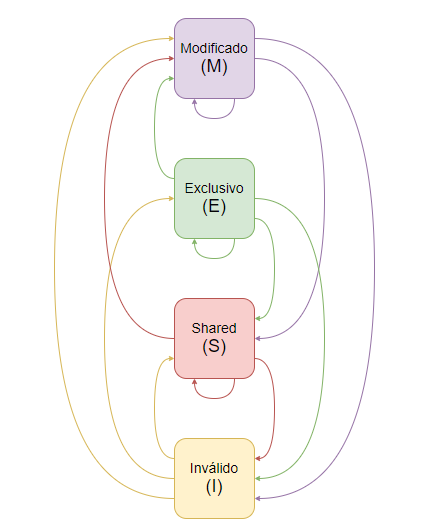

1.5.1. Coherencia

Un sistema de memoria es coherente si cualquier lectura de un dato devuelve el valor más reciente de ese dato. Procesadores que comparten el espacio de memoria pero tienen cachés individuales.

- Protocolo de fisgoneo: Control continuo del bus para monitorizar las operaciones con memoria

- Protocolo de snooping con invalidación: Se asegura que un procesador tiene acceso exclusivo a un dato antes de realizar una operación de escritura. Para ello, se invalidan el resto de copias que puedan existir del dato antes de escribir

- Protocolo MESI